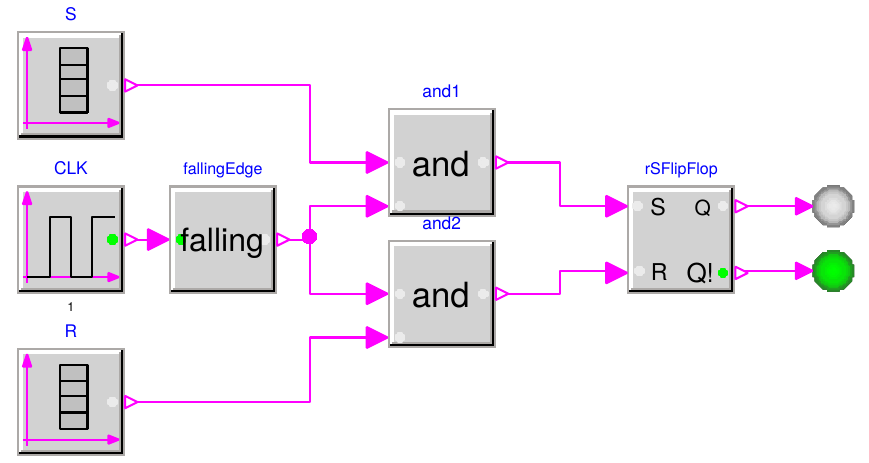

The triggered RS flip-flop

- Triggered flip-flops

- have an additional input (CLK)

- change state only, when CLK changes from true

to false ("falling edge")

- modeling in Simulink easy with a Trigger block

- Implementation in Modelica

- Falling edge block creates "infinitesimal" signal

- used to unlock the data inputs

- versions A/B according to static

flip-flop used

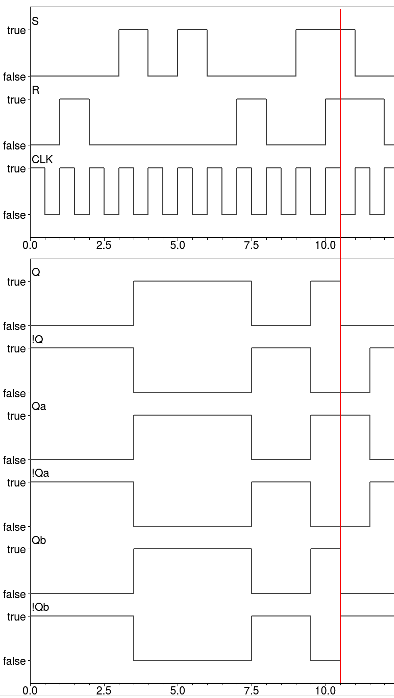

- Simulation results

- in Simulink (Q, !Q) exactly as expected

- in Modelica mostly identical results

- different behaviour at t = 10.5 + eps